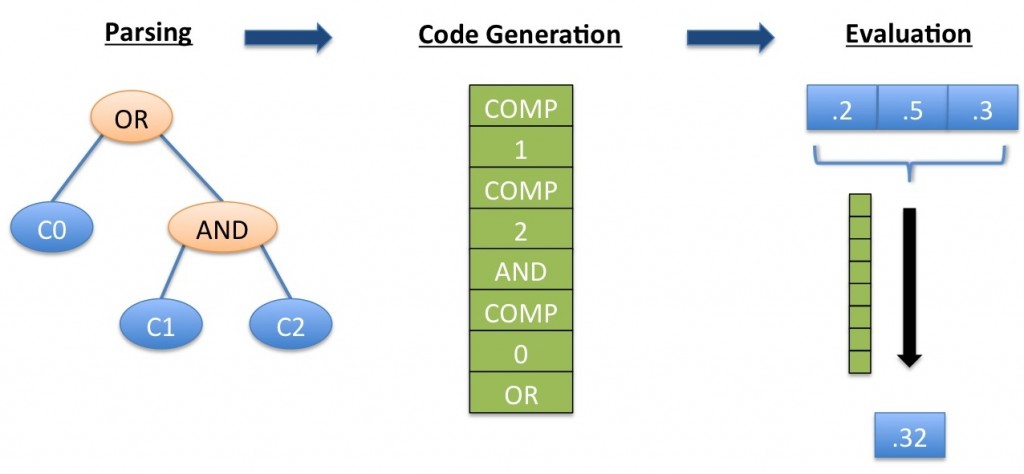

Readers are guided through a progression from a scalar fault tree code to one mapped effectively to Intel Xeon Phi with the open-source ispc (Intel SPMD Program Compiler). Fault trees express failure relationships between systems using Boolean logic to evaluate the vulnerability of systems based on component reliability, system redundancy, physical protection, and other — potentially domain-specific — factors. FTAs have been adopted by the defense, aerospace, nuclear, chemical, and other high-hazard industries as the primary methodology for understanding system vulnerability. Topic covered in this chapter of High Performance Parallelism Pearls include Thread Level Parallelism (TLP) using APIs such as OpenMP, CILK Plus, and Threading Building Blocks. In many cases, however, effective SIMD utilization is not as straightforward as multi-‐threading. A purely scalar code can only use about 1/16 th of the single precision FLOPs of a coprocessor, even while maintaining good work distribution among threads. Therefore, this chapter points out some characteristics about SIMD programming with ispc in the context of evaluating fault tree expressions.

Chapter Author

Jefferson Amstutz is a Software Engineer in the Applied Technology Operation of SURVICE Engineering Company. His work explores interactive visualization and high performance computing in support of applications for the Army Research Laboratory. Currently, he leverages Parallel Evaluation of advances in massively parallel computing architectures and interactive ray tracing to solve a variety of physics‐based simulation problems in domains such as ballistic vulnerability analysis, radio frequency propagation, and soft-body simulation. Prior to joining SURVICE in 2012, Amstutz was a student in the Department of Computer Science at Grove City College, where he completed his B.S. in Computer Science with a minor in Mathematics.

Click to see the overview article “Teaching The World About Intel Xeon Phi” that contains a list of TechEnablement links about why each chapter is considered a “Parallelism Pearl” plus information about James Reinders and Jim Jeffers, the editors of High Performance Parallelism Pearls.

Leave a Reply