Register early for Supercomputing 2014 in New Orleans and save up to $275. View the Technical Program online (and register for our tutorial!) The Technical Program fee includes admission to all conference sessions, exhibits, the Monday night Exhibits opening event, Thursday night event, and one copy of the SC14 proceedings. Click here to view the grid showing access to … [Read more...]

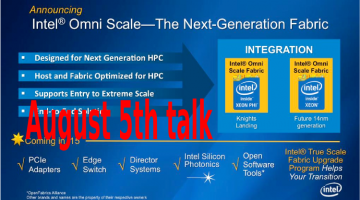

Intel Webinar About “Omni Scale” Next-Generation High-Performance Fabric and Future Directions

Register to attend the August 5th webinar by Joe Yaworski from the Intel Technical Computing Group titled, "High Performance Fabrics from Intel - Today and Tomorrow". Intel's thinking about network infrastructure will have a decided impact on the future of HPC given their recent wins on the NNSA (National Nuclear Safety Agency) 42 PF/s Trinity supercomputer plus the NERSC … [Read more...]

42 PF/s Trinity Supercomputer to Use Intel Knights Landing

First details on the National Nuclear Security Administration (NNSA) Trinity Supercomputer show that the 42 PF/s system costing $174M USD will run a combination of Intel Haswell and Knights Landing processors. In particular the Intel Xeon Phi devices will use Micron’s Hybrid Memory Cube technology, which will greatly help memory bandwidth and memory capacity limited … [Read more...]

TechEnablement Adds Funding Opportunity Posts via Dr. William Reynolds

TechEnablement is pleased to announce that Dr. William Reynolds PhD - an expert in applied scientific computing, funding proposals, and government research, - will be identifying pending funding opportunities for our readership. These posts will round out the TechEnablement content pool to (1) educate readers about the current technology, (2) plan both applications and … [Read more...]

ARM64 and x86 With OpenMP 4.0 For HPC and Enterprise in GNU and Possibly Clang

The OpenMP 4.0 specification is moving quickly to implementation through the GNU toolchain and Clang. TechEnablement reported that GNU 4.9.1 now supports OpenMP in C/C++ and Fortran plus we now have confirmation that OpenMP will run on ARM64 as well, or as Jakub Jelinek wrote, "All architectures where libgomp is supported (which is essentially all which have pthreads)." The … [Read more...]

GCC 4.9.1 Adds OpenMP 4.0 Fortran Support for Multicore

Jakub Jelinek <jakub at redhat dot com> posted on July 16th that the GCC 4.9.1 release now supports OpenMP 4.0 in Fortran (as well as C/C++). This is great news for multi-core programmers. GCC looks to be on-track to become the opensource platform that both Intel Xeon Phi and GPU programmers can use to to test pragma based programming. As reported on techEnablement.com, … [Read more...]

GCC likely to support both OpenACC and Intel Xeon Phi Offload Pragmas in 2015

It looks like GCC will be supporting both OpenACC and Intel Xeon Phi offload pragmas in future releases. Perhaps the GNU compiler chain will become the melting pot where OpenACC and OpenMP 4.0 pragmas merge to become a single unified syntax. According to Nathan Sidwell, Director of Sourcery Services at Mentor Embedded, their OpenACC effort is working to “make the underlying … [Read more...]

Intel Knights Landing: Claimed 4x An NVIDIA K40 (on some applications)

Joe Curley (Director of Marketing in the Technical Computing Group at Intel Corporation) just completed his webinar on BrightTalk, "The Faster Path to Discovery: New Details on the Intel® Xeon Phi™ Product Family" that disclosed new details on the upcoming Knights Landing massively=parallel chip including a claimed 4x performance improvement over the NVIDIA K40 on some … [Read more...]

Intel Knights Landing Webinar June 24

Microway is hosting a webinar, "The Faster Path to Discovery: New Details on the Intel® Xeon Phi™ Product Family" that will cover the next-generation Knights Landing processor on June 24. Register here to attend. … [Read more...]

TACC Intel Xeon Phi – MIC – User Group Meeting July 8-9

TACC is hosting a meeting of the Intel Xeon Phi user group (IXPug) in Austin, TX July 8-9, 2014. IXPug has been created to promote the exchange of user experiences in adopting and using the Phi processors. Registration is free and open until July 1, 2014. Attend IXPug to start or enhance your Xeon (X86) programming skills on the Intel Many Integrated Core (MIC) architecture, … [Read more...]