The ArrayFire GPU accelerated library software has made news by announcing they are moving to open source. Right now only the wrappers and examples that will bring more customers are currently open source. A business-savvy first move. Specifically, the ArrayFire website states, " ... it’s neither simple nor straightforward to take a closed software Open Source. Earlier … [Read more...]

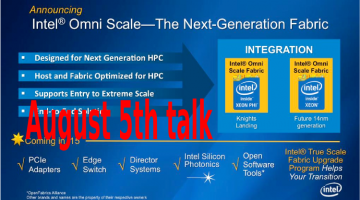

Intel Webinar About “Omni Scale” Next-Generation High-Performance Fabric and Future Directions

Register to attend the August 5th webinar by Joe Yaworski from the Intel Technical Computing Group titled, "High Performance Fabrics from Intel - Today and Tomorrow". Intel's thinking about network infrastructure will have a decided impact on the future of HPC given their recent wins on the NNSA (National Nuclear Safety Agency) 42 PF/s Trinity supercomputer plus the NERSC … [Read more...]

Model Validation: Darth Vader for President

Too good to pass up (and never forget the importance of validation!): The website FiveThirtyEight (a wonderful statistical analysis news site) reported that the data from their article Luke Skywalker vs. Hillary Clinton was further analyzed by Christopher Ingraham at the Wonkblog, 'Walter Hickey on the popularity of “Star Wars” characters' with the addition … [Read more...]

Linus Torvalds Says Fix GCC 4.9 Code Generation!

Phoronix picked up Linus Torvalds' providing some not so gentle feedback on GCC 4.9. GCC 4.9 supports OpenMP 4.0. Apparently the latest GNU compiler is doing some silly spilling of CPU registers (including constants!) that caused a random panic in a load balance function with the in-development Linux 3.16 kernel. On a comparative note, GCC just received … [Read more...]

TechEnablement Adds Funding Opportunity Posts via Dr. William Reynolds

TechEnablement is pleased to announce that Dr. William Reynolds PhD - an expert in applied scientific computing, funding proposals, and government research, - will be identifying pending funding opportunities for our readership. These posts will round out the TechEnablement content pool to (1) educate readers about the current technology, (2) plan both applications and … [Read more...]

ARM64 and x86 With OpenMP 4.0 For HPC and Enterprise in GNU and Possibly Clang

The OpenMP 4.0 specification is moving quickly to implementation through the GNU toolchain and Clang. TechEnablement reported that GNU 4.9.1 now supports OpenMP in C/C++ and Fortran plus we now have confirmation that OpenMP will run on ARM64 as well, or as Jakub Jelinek wrote, "All architectures where libgomp is supported (which is essentially all which have pthreads)." The … [Read more...]

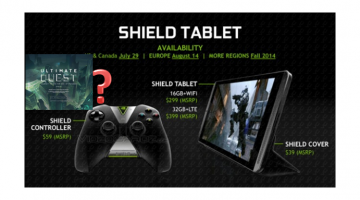

NVIDIA Shield 2 will be a tablet (with stylus) as well as a gaming device!

It's looks like it is true (and it can now be ordered), the K1-powered Shield 2 Gaming console will also be an 8" tablet! What a cool idea! This will be a CUDA/Gamers/Tablet/(cellphone?) honey of a device. (July 22: It's available now!). NVIDIA has created a tweet-based game "Ultimate Quest" in what is believed to be a promotion for the Shield 2. Click on the image below … [Read more...]

Assessing ROI in the Cloud For HPC and Enterprise

Just in time for ISC 2014! My latest Scientific Computing article, "Assessing ROI in the Cloud For HPC and Enterprise" that addresses the complicated decision, "to purchase infrastructure or run remotely in the cloud?" … [Read more...]

Women Who Code – Google’s $50M Program Kicks Off

Just weeks after releasing its first diversity report, Google is backing a new effort with $50M to bring more women into computer science. The new program is called Made with Code, which includes a mix of coding projects, partnerships with youth organizations to get more females involved in creating and writing computer software. This is just the latest effort by … [Read more...]

Intel Announces Xeon CPU + FPGA in a Chip

With ARM64 a given, Intel has been looking to increase market penetration through chip customization. June 8th Intel revealed plans to manufacture a new (as yet unnamed) server Xeon chip that contains an integrated FPGA. The FPGA and CPU will have coherent access to memory. The combination chip will be package compatible with the existing Xeon E5 line. Intel mentions that … [Read more...]