NERSC published an informative preparatory article for programming the forthcoming Cori supercomputer that notes each Intel Xeon Phi “Knight’s Landing” (KNL) devices will be running in a “self-hosted” mode, meaning that there will be no host/traditional processor. Everything – including the operating system – will run on KNL. This eliminates concerns about data movement as there is no “offload” mode, but the article notes that performance will be determined by the performance of the memory subsystem that holds the data and expressing enough fine-grained parallelism to keep the 60+ KNL cores busy.

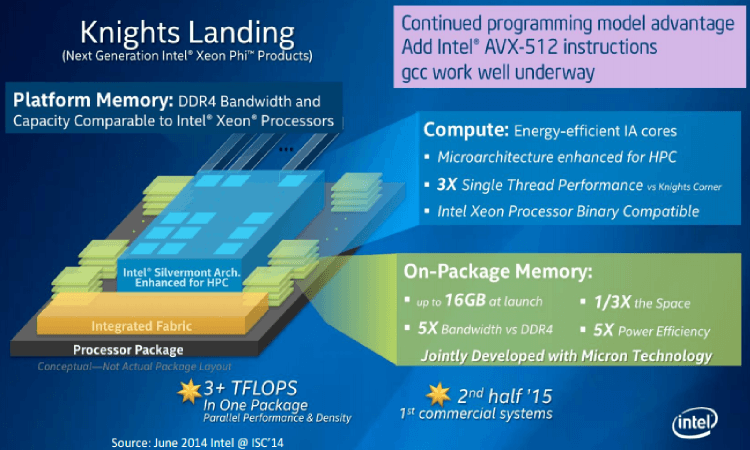

Intel notes that the KNL memory system will utilize up to 16 GB of “on-package” or “High Bandwidth Memory” (HBM), which is claimed to have 5x the bandwidth of DDR4 memory (see slide below). It is very likely that many currently memory bandwidth bound applications KNC will see a large performance improvement on KNL purely as a result of HBM memory. Any data that does not fit into the HBM will need to be fetched from traditional DRAM and likely incur a greater than 5x performance penalty.

Leave a Reply