Twitter is a fantastic news source and provider of billions of noisy, needle-in-the-haystack tweets to confound data-scientists and delight analysts plus commercial marketing efforts. Interactivity with billions of data items is key to developing, understanding, and validating analysis. (Validation is emphasized as Google was recently fingered by IEEE Spectrum for biased … [Read more...]

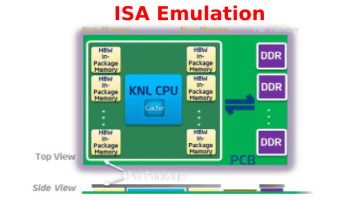

Latest Intel SDE Emulates New ISA Instructions For Knights Landing

Intel has released a new version of the Intel SDE (Software Development Emulator) so that customers can start working with upcoming instruction set extensions like AVX-512 for Knights Landing. The SDE can be downloaded after accepting a user agreement and used on Windows, Linux, and OS. It can also be used with the GNU gcc. The current version is 7.2 released on July 29, … [Read more...]

FabricEngine Leverages Python and LLVM For Digital Content Creation Everywhere

A company called FabricEngine (http://fabricengine.com) is leveraging the power of LLVM and Python to compile optimized code for Digital Content Creation (DCC) that can run on multicore and GPUs. Products like these demonstrate the acceptance of Python and LLVM into commercial/enterprise high-performance HPC applications just like PyFR and deep-learning. Integrated with … [Read more...]

Altera OpenCL Programmable FPGA Talks QPI, HMC, and 100G Optical Interconnect

At IDF14, Altera demonstrated some useful technology for FPGA and OpenCL FPGA developers including: (1) A Stratix® V FPGA driving a 100G optical link, (2) Micron Hybrid-Memory Cube interoperability, (3) OpenCL applications, and a biggie (4) QPI linking to an Intel Xeon Processor. This looks like an interesting platform for real-time OpenCL/FPGA development. The latter … [Read more...]

GCC 5.0 Provides Full Cilk Plus Support

GNU has announced that GCC 5.0 will provide full support for Cilk Plus. Cilk Plus is an extension to the C and C++ languages to support data and task parallelism on multi-core, vector and Intel Xeon Phi coprocessors.It is reputed to be quite efficient and looks to be easy to use. The Intel icc compiler has supported Cilk Plus for years. GNU support now makes Cilk Plus available … [Read more...]

Dongarra Gives Deep-Learning a Python Interface With RaPyDLI

An NSF-funded project called "Rapid Python Deep Learning Infrastructure", or RaPyDLI received nearly $1 million in NSF grants. The project led by supercomputing luminaries Jack Dongarra (University of Tennessee) and Geoffrey Fox (Indiana University) along with Andrew Ng (Stanford, Baidu and Coursera) will allow users to program deep learning models in Python and port them to … [Read more...]

Lustre Delivers 10x the Bandwidth of NFS on Intel Xeon Phi

Lustre on Intel Xeon Phi delivered 10x the bandwidth of NFS as reported in the 2014 Lustre User Group (LUG) presentation "Running Native Lustre* Client inside Intel® Xeon Phi™ coprocessor" by Dmitry Eremin, Zhiqi Tao and Gabriele Paciucci of Intel Corporation. Network file systems are essential to the current generation of Knights Corner Intel Xeon Phi coprocessors because the … [Read more...]

Shared Memory is Simple on Intel Xeon Phi – supports STL!

Shared memory on Intel Xeon Phi, in OpenCL, and CUDA (via managed memory) greatly simplifies programming by eliminating the need to explicitly define all data transfers between host and device memory. Once these implementations mature, it is likely they will become the standard API that programmers use to access data on both Intel Xeon Phi and GPUs. (They also naturally support … [Read more...]

Intel SPMD Compiler (ISPC) for Xeon and Xeon Phi

When #pragma SIMD is not enough, companies and projects such as Intel, Embree, Dreamworks, Pixar, Autodesk, and SURFsara are looking to the freely available Intel SPMD Program Compiler (ispc) to achieve high vector performance on Xeon and Intel Xeon Phi devices. ISPC is LLVM-based and designed to exploit Intel SIMD architectures … [Read more...]

NESAP – The NERSC Exascale Science Application Program – Eight Post-doc Positions to be Filled

DOE’s Office of Science is the single largest supporter of basic research in the physical sciences in the United States, and is working to address some of the most pressing challenges of our time. NERSC is currently hiring eight post-docs to assist this effort. The NESAP program at NERSC addresses the software issues that will arise as scientists adapt their applications to … [Read more...]